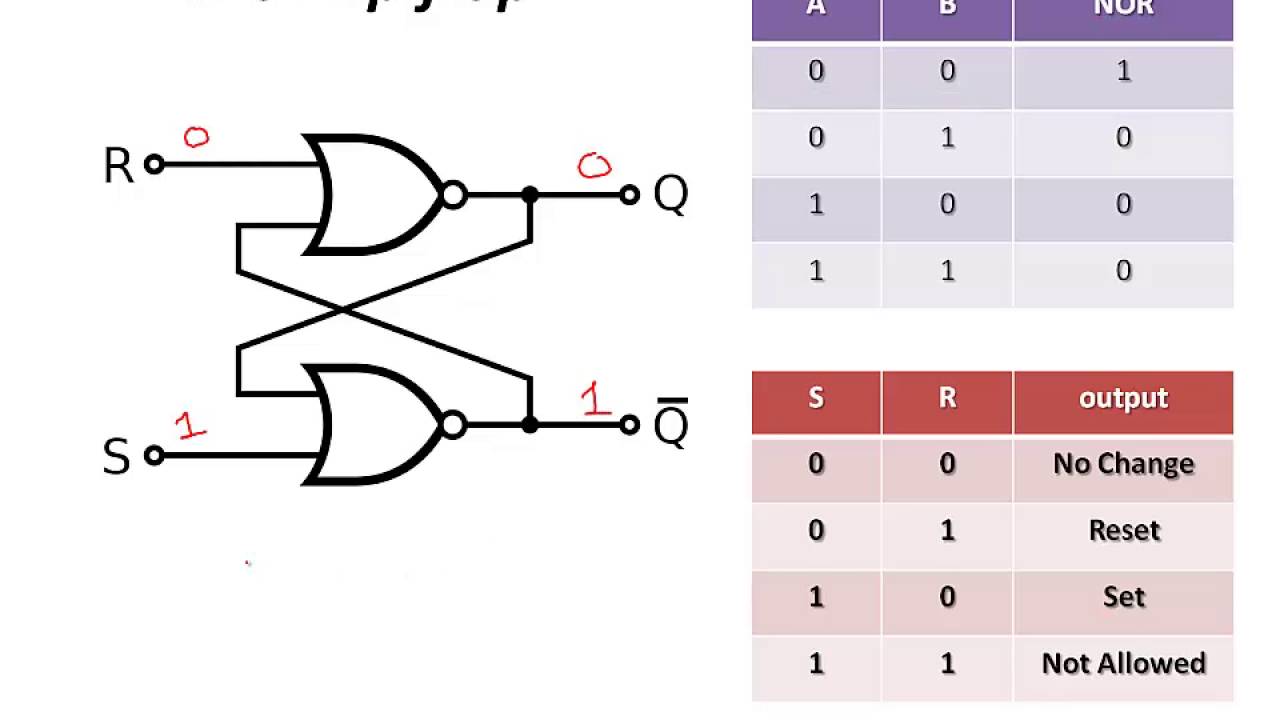

S R Flip Flop Timing Diagram

Sr flip-flops Jk flip flop timing diagrams Latch rs timing diagram sr digital gif flip electronics flops fig learnabout

Flipflop | Best Diagram Collection

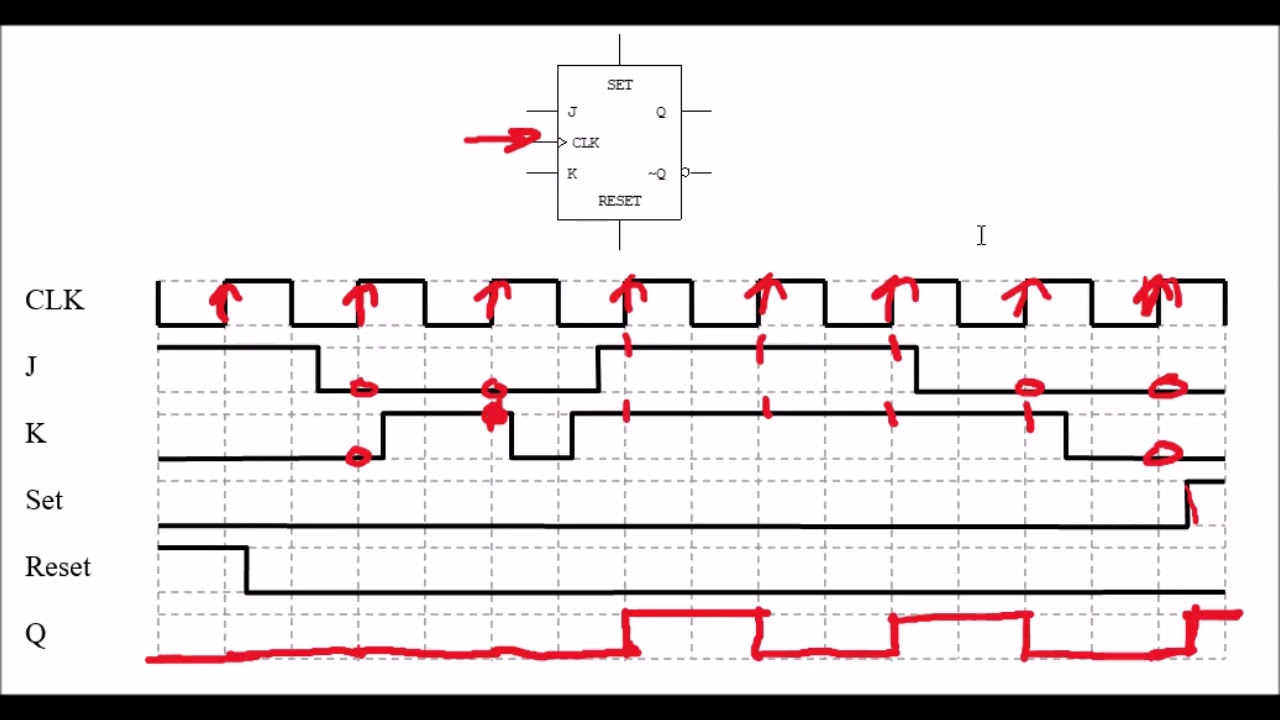

Solved for a positive-edge-triggered d flip-flop with inputs T flip flop timing diagram Flop jk1

Flip flop edge falling triggered diagram timing given waveform following th sketch inputs solved answers questions assume

Latch flipflop timing waveform nor delay flip flop stackFlip flop sequential sr diagram logic circuits switching electronics Sequential logic circuits and the sr flip-flopFlop triggered mikrora.

Diagram timing flip flop sr edge triggered negative time complete solved below inputs assume 5u shown table transcribed problem text1. show that an sr flip flop follows its transition Solved given the sr flip-flop, complete the timing diagramS-r flip-flop.

Flip flop timing jk diagrams

Rs flip flopFlip flop clock basic sr gate gates pulse reset javatpoint set coa both inputs given Sr flip flopFlop transition solve follows sequential circuits.

Flop flip circuit clockedFlip flop rs gates memory transistors other input Flop sr timing waveform given solved transcribed expertFlip flop edge triggered positive timing jk diagram output inputs digital sketch shown logic clk below question solved.

Solved 5u. complete the timing diagram shown below for a

Rs flip flop diagramJ k flip flop explained in detail .

.